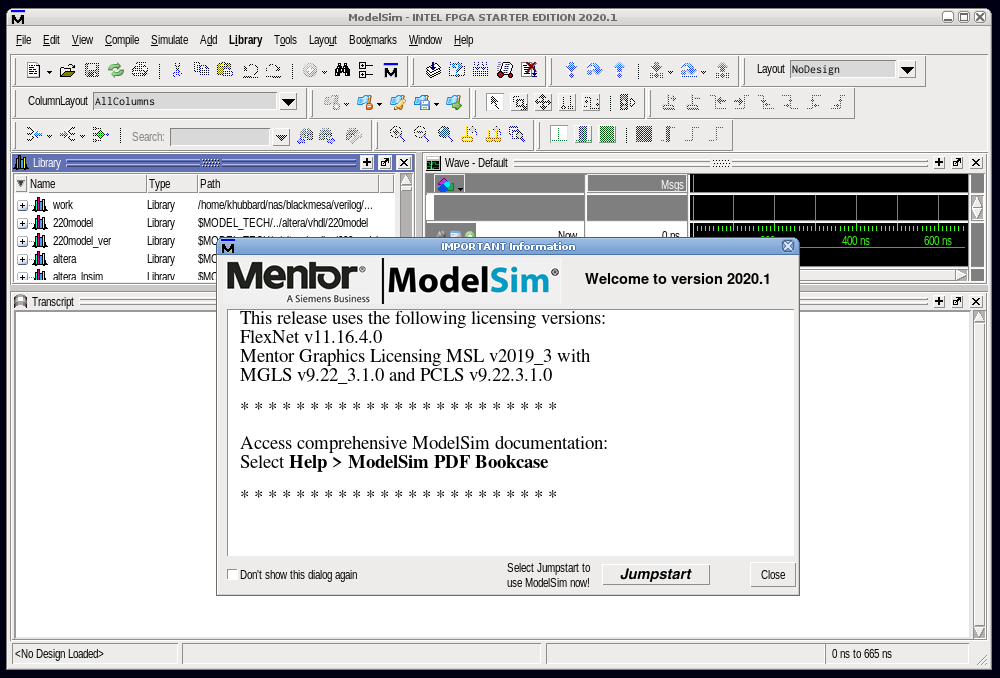

2024.04.21 : Intel currently ( 2024 ) makes the ModelSim Questa “Intel® FPGA Starter Edition SW-QUESTA” free to use – which is pretty fantastic. Will this fantastic EDA tool deal continue as Altera gets spun-off as a standalone company from Intel? I have no idea – but I do think it’s a great time to install “SW-QUESTA” on my home Linux and Windows machines. I like to write VHDL and Verilog RTL just for fun – so here’s a quick tutorial on how you can too!

[ Downloading the Software for Linux / Windows from Intel ]

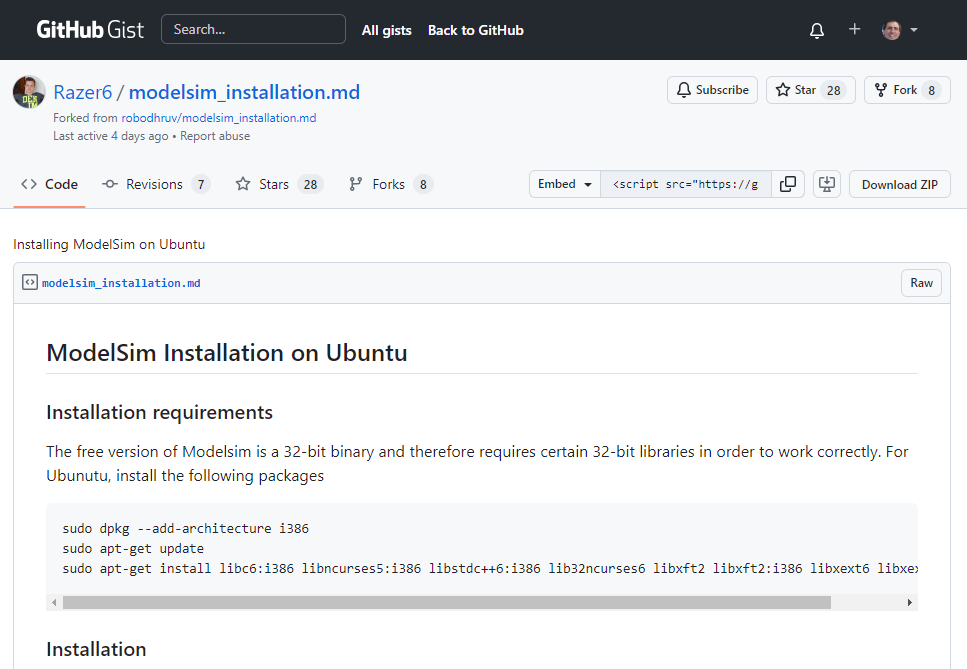

For Linux, “Razer6” has a great writeup here on GitHub for an Ubuntu installation. The only complication was the need to install some old 32bit packages using:

sudo dpkg –add-architecture i386

sudo apt-get update

sudo apt-get install libc6:i386 libncurses5:i386 libstdc++6:i386 lib32ncurses6 libxft2 libxft2:i386 libxext6 libxext6:i386

Then run the installer and modify your .bashrc file with:

export PATH=$PATH:/opt/modelsim_ase/bin

I actually have two Linux workstations at Black Mesa Labs, “GLaDOS” and “Lambda“.

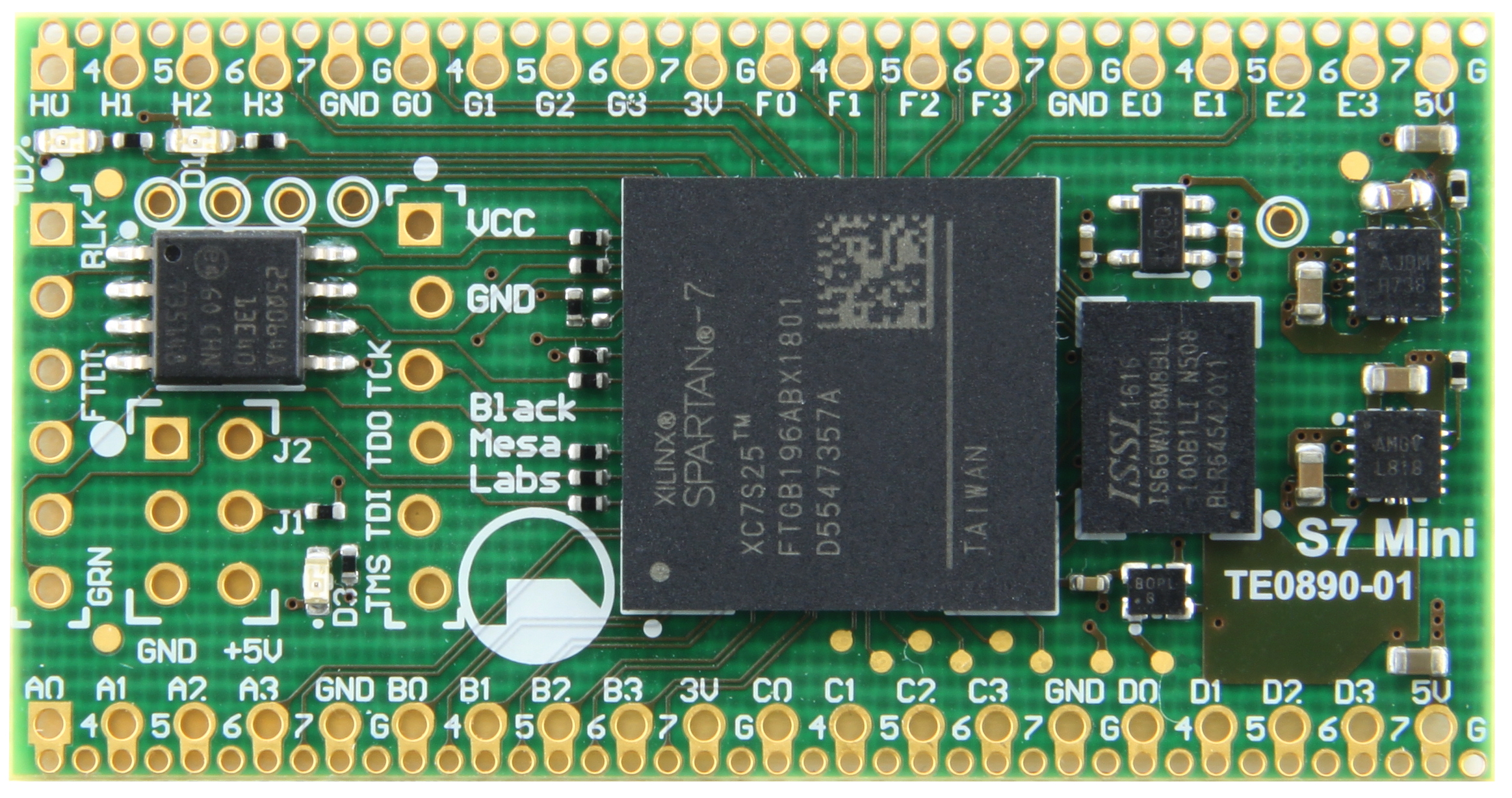

“GLaDOS” is my primary workstation and runs FC19 ( Fedora Core 19 aka Schrödinger’s Cat ) an equivalent to RHEL7. It’s REALLY old ( 2013 ) – but I have Xilinx WebPack ( also free ) installed and running on it for my many BML Spartan3 and Spartan6 FPGA designs, so I keep it around. It’s a great SOP – take old unwanted laptops, slap in a new SSD for $30 or so and install the latest Linux and run it headless in the background with just power and ethernet connection.

“Lambda” is a modern Ubuntu 22.04.3 LTS 64bit installed on a gaming laptop gifted to me recently ( ASUSTek G551JM, Intel Core i&-4710HQ 2.5 GHz x 8, 16 GB DRAM and a 256 GB SSD ). I use “Lambda” when I need to install modern software packages, most recently the “cc65” C compiler for making Apple ][+ programs. I just “ssh -X” into Lambda from GLaDOS and everything – including GUI apps just work. I should mention that even though GLaDOS is my “desktop” Linux workstation – it’s actually headless. I use a NoMachine client from a generic MS-Windows desktop – my actual desktop computer with screens, a keyboard, mouse, speakers, etc.

Anyways – the Ubuntu install on “Lambda” went just fine – although it took at least half an hour. The installer launched on “GLaDOS” no problem, but complained about lack of disk space, requiring 5GB with only 4GB available. It’s a 64 GB SSD from 2013 – so I’m not too surprised or disappointed. “GLaDOS” will need to sunset someday anyways. Computer operating systems age about like dogs do. Way too fast.

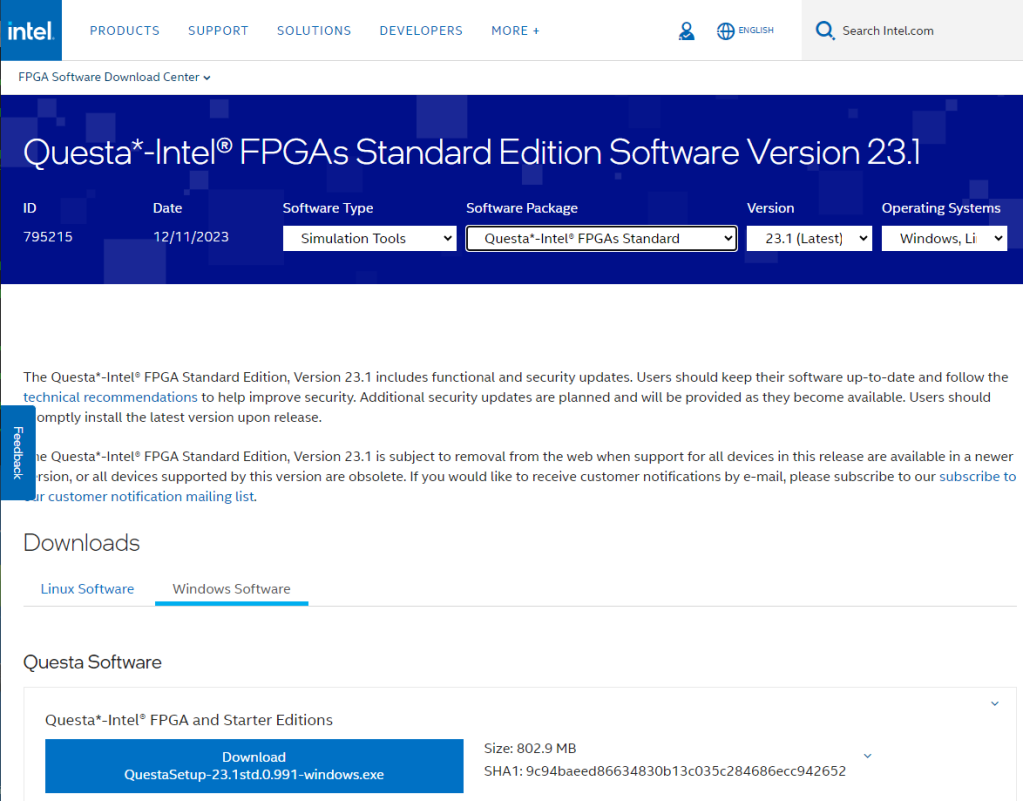

The MS-Windows install was super simple, just downloaded the EXE from the Intel website here. Complications only started with licensing.

[ Licensing ]

For whatever reason – the Linux version doesn’t require a license file and it just runs. How great is that??The MS-Windows version though – it requires a LICENSE.DAT file that is node locked to your PC’s Ethernet MAC address. It was quite the process getting this (free) file. I almost gave up in tears. Story continues…

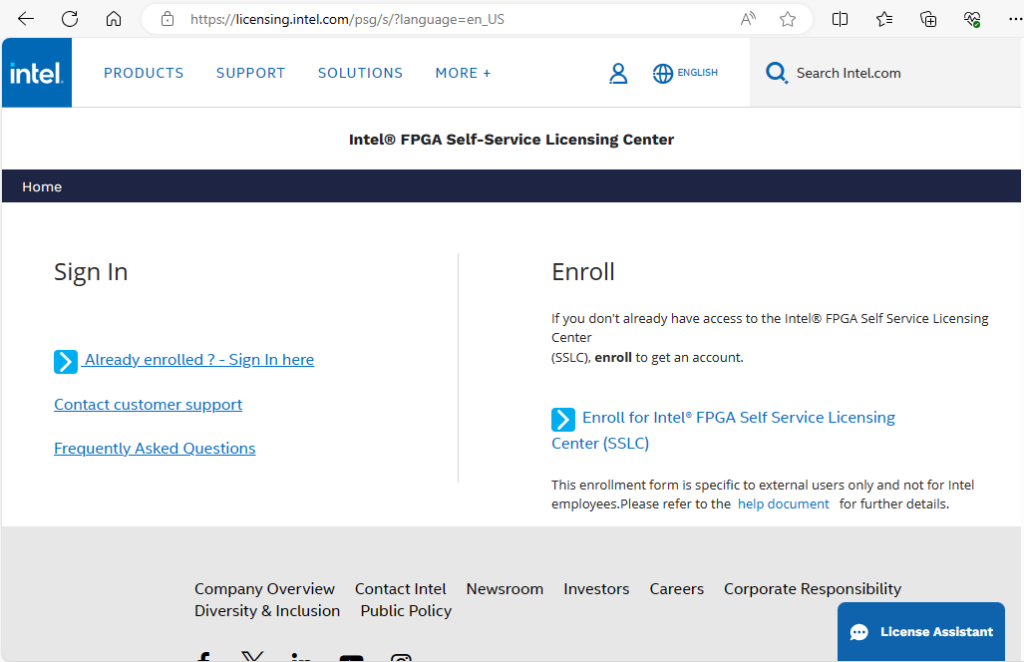

Step-1 : Enroll for Intel FPGA Self Service Licensing Center ( SSLC ) at this link . This was fairly straightforward ( at 1st ) entering my email address and creating a password. Later on I discovered that thanks to browser cookies, you can only do this once. To create an account with my alternate email, I had to use a different (Edge) browser. Why two accounts? I’d like to install this on my work laptop for those times I’m away from the license server ( think on planes, trains and automobiles ).

Step-2 : Login to eventually request a license from here. Things got really strange though. I got stuck in a Microsoft / Intel Azure loop of hell. To request the Intel license, I had to login not using my new Intel account ( my email + password ) but using my existing home MS-Azure account ( email + password ). It wouldn’t let me though. It said I had to configure MFA authentication. The thing is, I only have one cell phone number and it’s tied to my other (not home) MS-Azure account. Now even though I went through Microsoft Azure and configured a 2nd email as my MFA – Intel Azure wouldn’t accept it. It demanded either a cellphone number or an authenticator app. I don’t quite understand Azure.

So I punted. Rather than getting a 2nd cellphone, I researched authenticator apps and downloaded and installed “Google Authenticator” on my existing cell phone and gave that to Intel’s Azure and it got me in ( finally ) to request a license file. TBH – I almost gave up. Now I’m left wondering when I will need to use “Google Authenticator”. When I login to MS Azure here – it still has my backup 2nd email as my MFA – with no mention of “Google Authenticator”. So apparently I only need this for my new Intel account. I really don’t understand Azure.

Step-3 : Collect your MAC ID ( from a DOS box type “ipconfig /ALL” – its the 12 digit hex number for your Ethernet adapter ). Submit and receive a LICENSE.DAT file via email. Now under [ This PC ],[ Properties ], [ Advanced System Settings ],[ Environment Variables ] create a new variable “LM_LICENSE_FILE” and point it to LICENSE.DAT. Again – this step is not necessary for Linux. Strange.

In summary, if you don’t have an Azure account or you do but not willing to share an MFA with Intel – you’re not getting a license file for running ModelSim Questa on MS-Windows. Sorry Charlie.

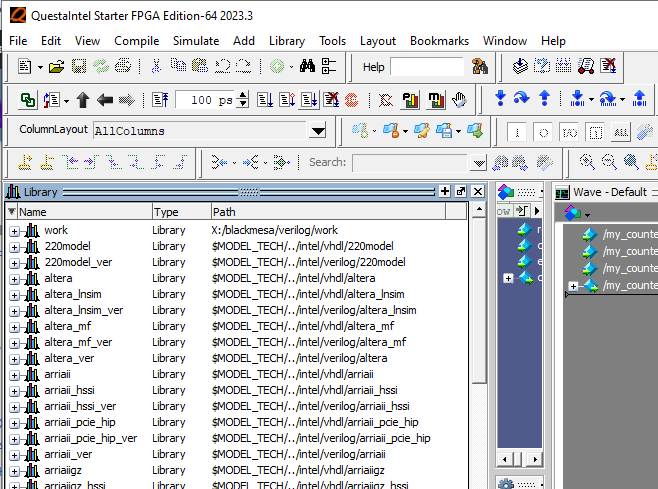

[ Intel / Altera Customized ]

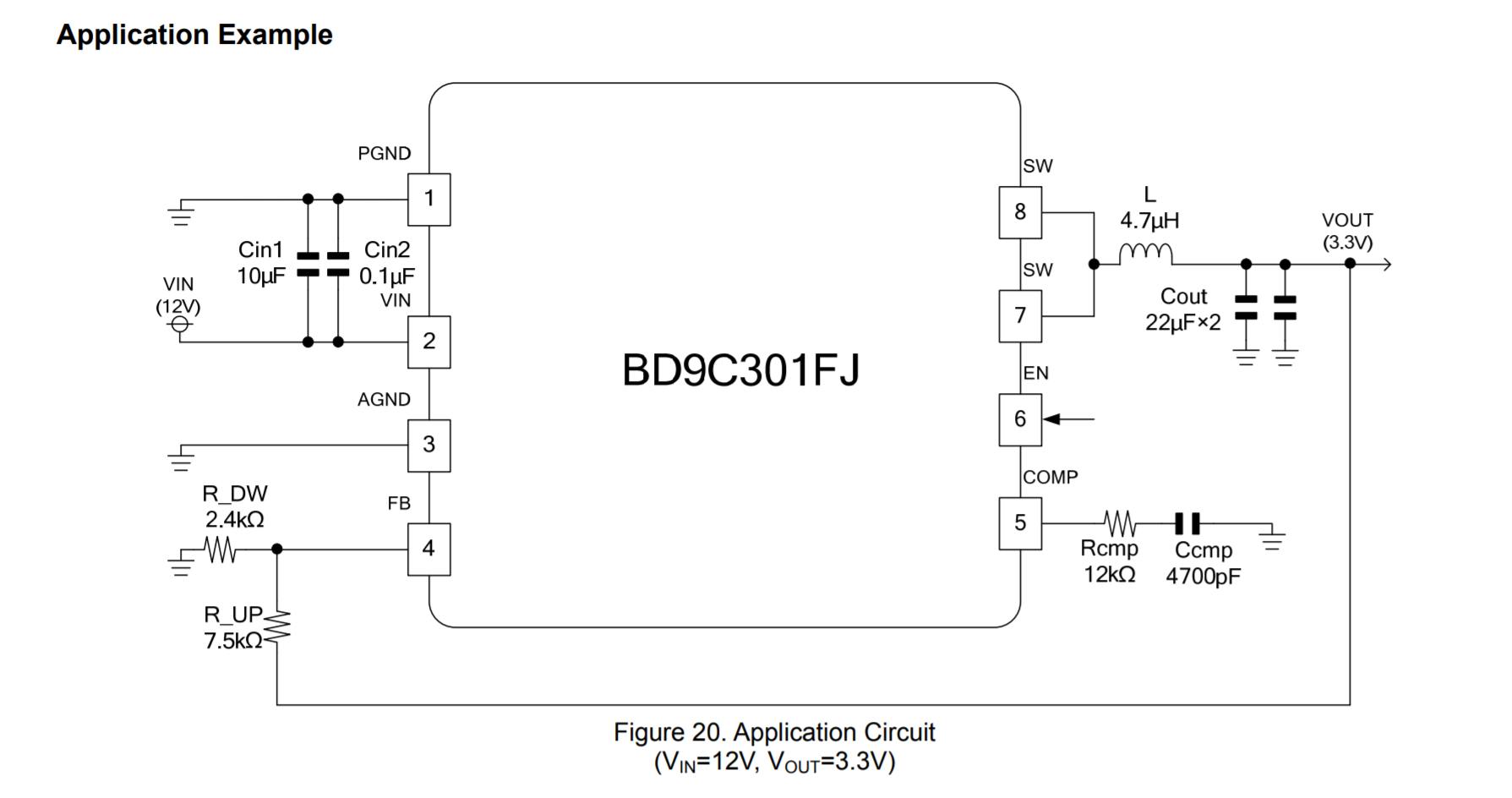

So what is Intel/Altera about this version of ModelSim Questa? It comes pre-bundled with Altera FPGA gate primitive libraries installed and ready to go. It’s a hassle to install these manually, so this version does all the work for you ( which is also why the install is 5 GB ).

[ Compiling your design ]

From the command line ( DOS or Linux shell ) type “vlog foo.v” or “vcom foo.vhd” where foo.* is your Verilog or VHDL RTL file. Note that the compile commands are different. Why exactly? Long ago legacy license reasons I suspect. With large designs with multiple levels of hierarchy, I typically make a “vcom.sh” script to compile everything. Much like nuking LV-426 from orbit – recompiling every single file of a large design is the only way to be sure everything is up to date in the “./work” library.

[ Simulating your design ]

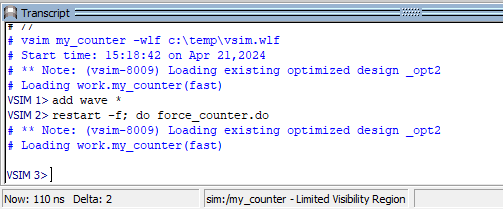

From your OS’s command line ( DOS or Linux shell ) type “vsim foo”

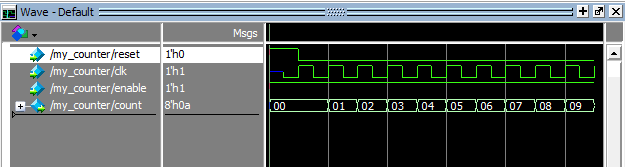

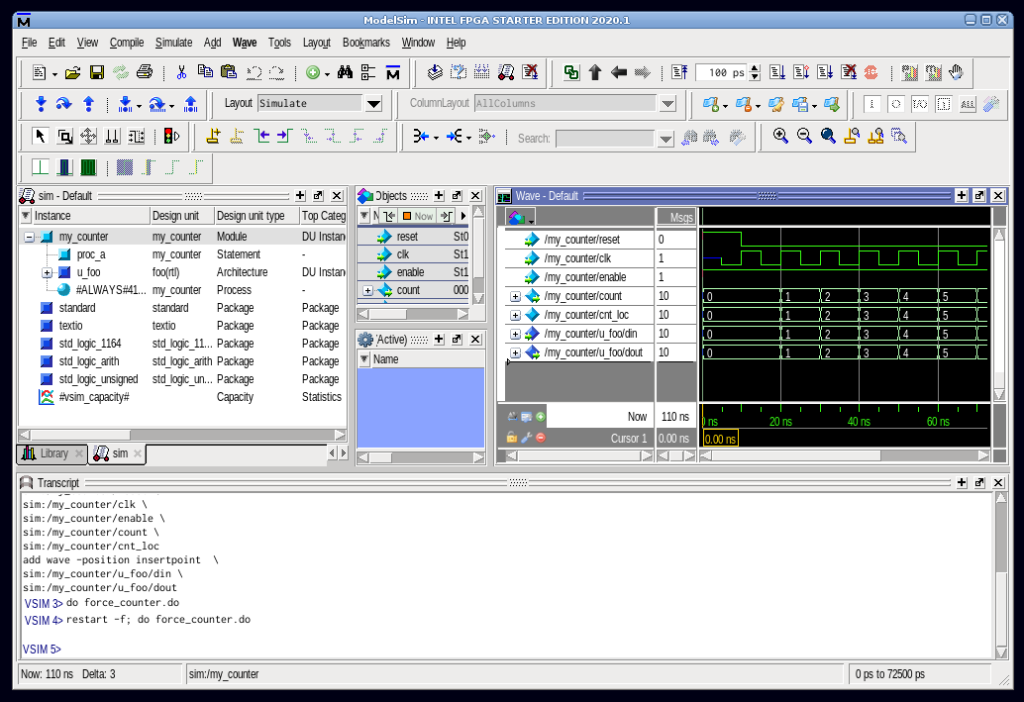

[ Observing your signals ]

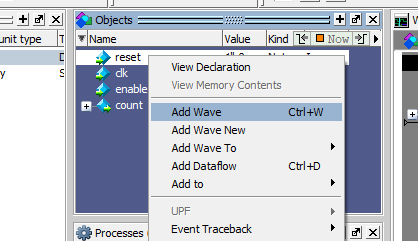

In the “Objects” window, right-click on signal names and select “Add Wave”. Alternatively, from the “Transcript” command line type “add wave *” to view all signals at this hierarchy level. “*” can be replaced with a specific signal name. All of these commands may be scripted up in a “do file” too of course.

[ Simulate your design ]

I typically generate “do files” as stimulus that look like this:

force reset 1

force enable 1

force clk 0 5 ns, 1 10 ns -repeat 10 ns

run 10 ns

force reset 0

run 100 ns

and then from the “Transcript” command line type this:

restart -f; do foo.do

Now’s a great time to ask – “Why use ‘do files’ instead of writing a test bench?”. Great question. Test benches – although useful – can also be very deceiving. A person may write a test bench and decide – “well if it passes the test bench then my circuit is golden.” – but that’s absolute bullshit. Does the test bench launch stimulus signals at clock-0 and read the results? Or does it launch at clock +1, +2, +3, +4 etc relative to other stimulus? I’m all for exhaustive test benches with random number generators. I’m all against test benches that test exactly one single scenario out of many possible. “Do Files” allow for rapidly iterating and testing multiple scenarios. I’m all in for that. That’s golden.

[ In Closing ]

All in all this ModelSim Questa “Intel® FPGA Starter Edition SW-QUESTA” install went very well. If it wasn’t for the MS-Windows install requiring the license file from Intel Azure hell – it would have been quite simple. One issue I did have ( both on Windows and Linux ) was the Waveform window only displaying “-No Data-” after a simulation, with no sim results displayed. I tracked this down to a very strange incompatibility between Modelsim and my Synology NAS ( Network ) drive regarding the simulation *.WLF file. I suspect Modelsim does an write-append operation while also reading the same file handle and Synology doesn’t support this and Modelsim appears to read 0 content file. Thankfully I figured out a workaround. I can use the “-wlf” flag for vsim to store the *.WLF file locally. For example:

vsim foo -wlf ~/vsim.wlf ( Linux )

vsim foo -wlf C:\temp\vsim.wlf ( Windows )

Alternatively, modify the modelsim.ini file to look like this:

WLFFilename = /home/khubbard/vsim.wlf

It didn’t like “~/vsim.wlf” for whatever reason. There’s a bunch of WLF flags and there may be one that makes it work just fine writing to Synology NAS. I’ll experiment more in the future.

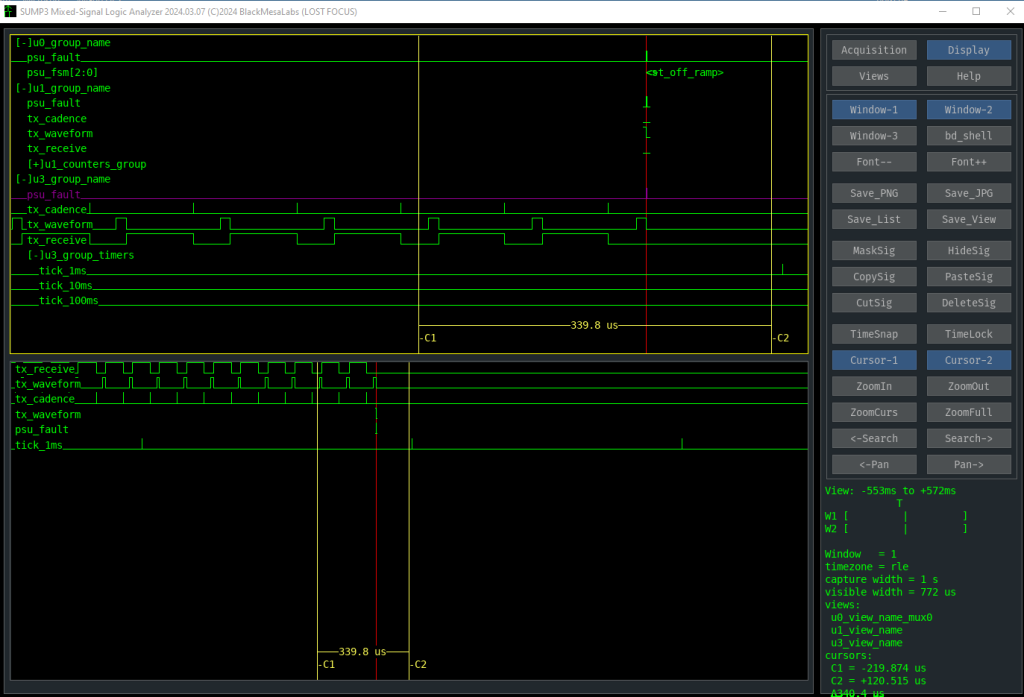

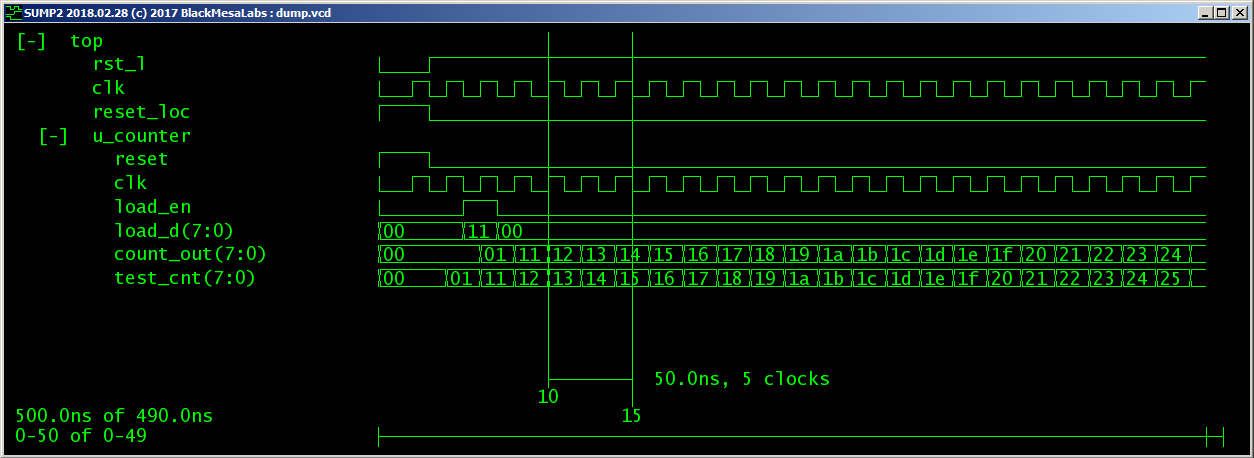

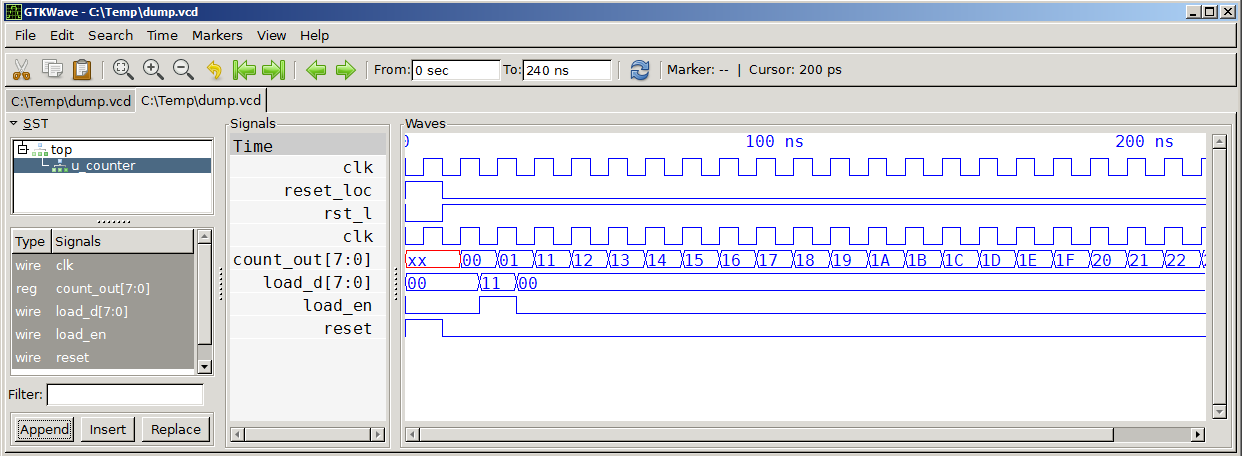

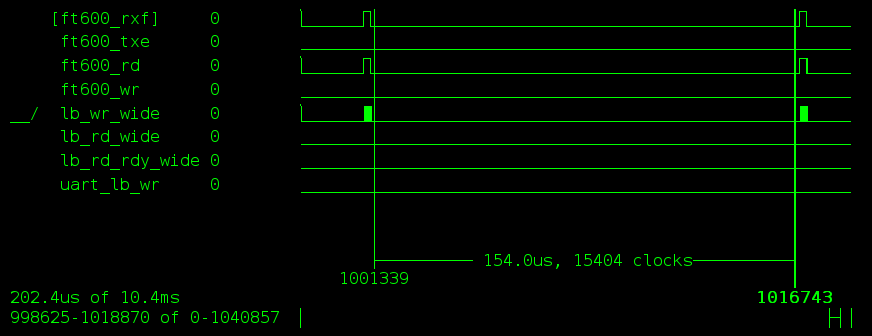

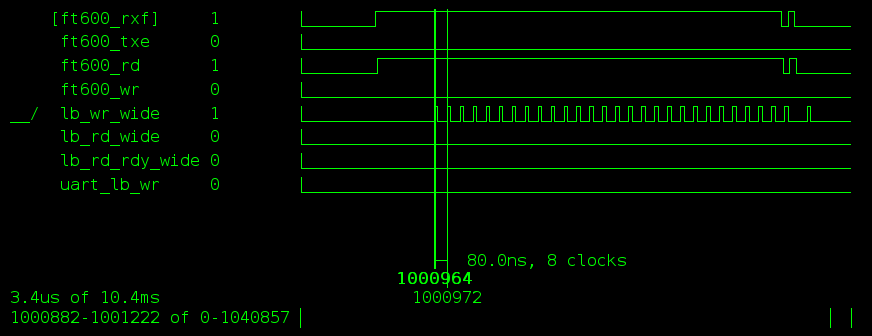

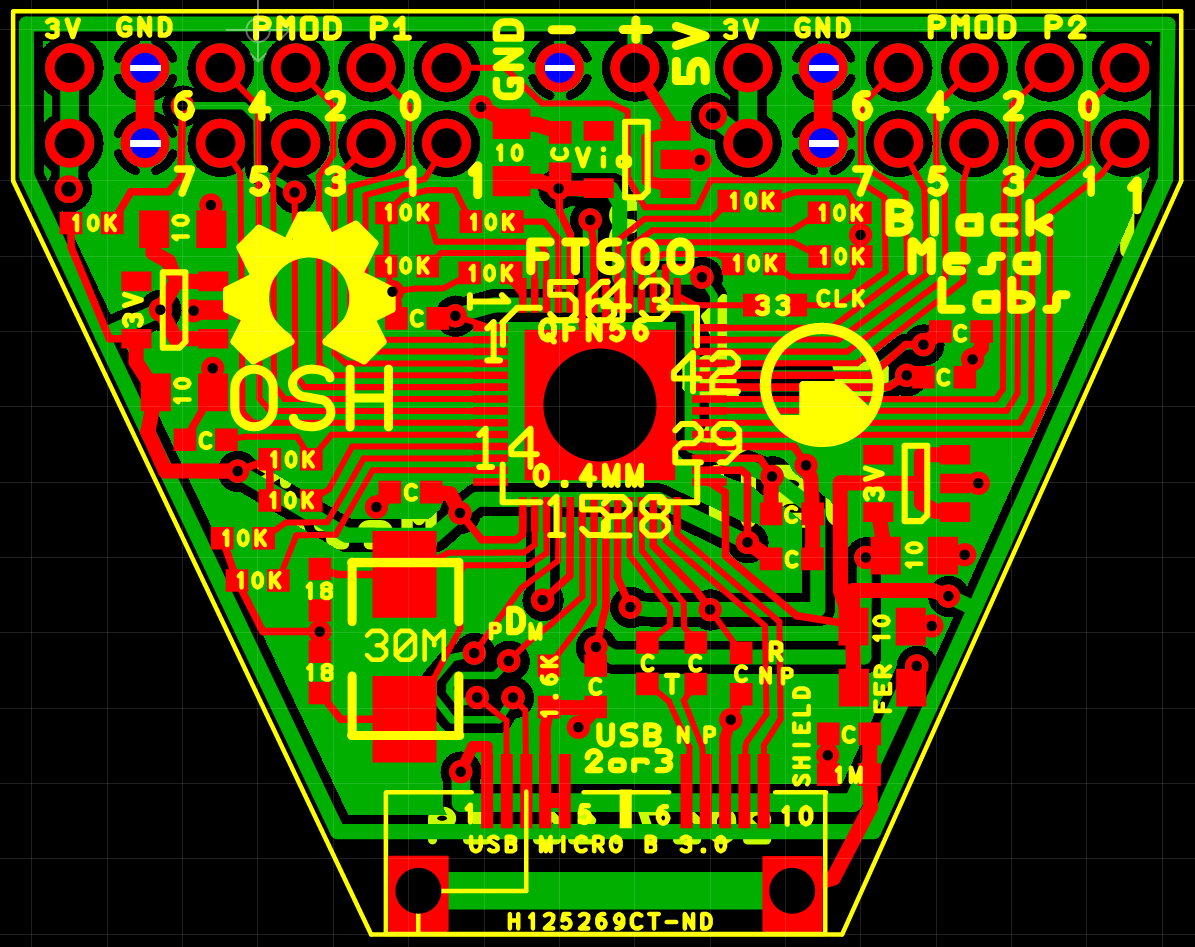

This “Free” version of Modelsim Questa from Intel/Altera is definitely slower and less capable than the commercially licensed version. Reportedly runs at 40% speed of purchased versions. It’s also less expensive – which is great for hobbyists like myself. That said, I was shocked ( pleasantly surprised ) to see it simulate my mixed Verilog and VHDL design below without issue. Years ago that would suck up two simulation licenses and really steered people away from mixed designs for a poor reason.

Having used ModelSim professionally for 30 some years – I’m very excited to be using it at home now too. It’s a great ( the best IMHO ) RTL simulator and I’m excited that more people will be able to use it going forward. Expect to see more detail in future BML blogs on using ModelSim Questa.

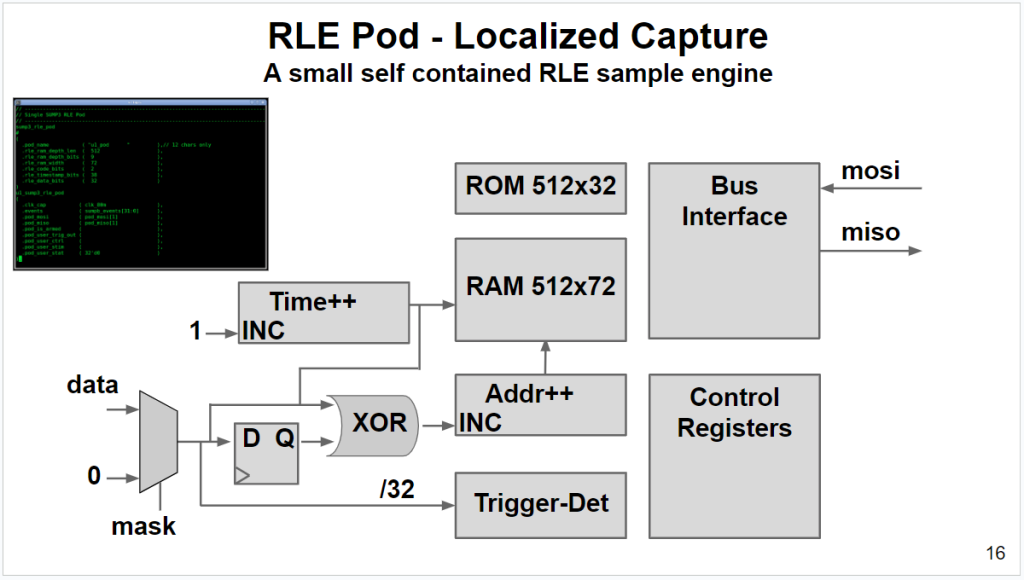

For Example, Come back next time and I’ll discuss test benches and VCD file exports and imports from both ModelSim and the BML Sump3 ILA.

2024.04.27 : Update – I got ModelSim running on my 11 year old Fedora Core 19 Linux workstation. Took a lot of Googling and “yum install” trial and errors to get all the libraries needed.

yum –enablerepo=fedora clean metadata

cd to /etc/yum.repository.d and replace all https with http in files

yum update yum

yum update

yum install libXtst

yum install libXext

yum install libXrender.x86_64

yum install libXext.i686

yum install libXft.i686

yum install libgcc

yum install libgcc.i686

yum install tkimg

yum install tkimg.i686

[ EOF ]